Vol. 53 No. 12 Dec. 2013

doi:10.3969/j.issn.1001-893x.2013.12.010

## 一种改进的多模数字下变频结构及其 FPGA 实现\*

## 张庭伟\*\*,袁正午,周 牧,田增山

(重庆邮电大学 移动通信技术重庆市重点实验室,重庆 400065)

摘 要:针对目前多种通信模式的共存和发展趋势,对传统 DDC 结构进行改进,以适用于多模系统。 提出了多模数字下变频改进结构与参数设计,完成了各模块 Verilog 代码编写和 Modelsim 仿真,并对 Modelsim 仿真结果进行分析和验证,验证了改进数字下变频的可行性;最后将代码移植到 FPGA,并 结合 ETTUS 射频板、自主设计的中频板以及友晶 TR4 FPGA 开发板多模硬件平台进行了板级调试, 验证了多模功能的可行性,充分证明该结构能兼容 WCDMA 和 TD-LTE 两种模式,具有较高的实用 性和通用性。

关键词:软件无线电:多模终端:数字下变频:现场可编程门阵列:中频

中图分类号:TN929.5 文献标志码:A 文章编号:1001-893X(2013)12-1592-06

# An Improved Multimode Digital Down Converter Structure and its FPGA Implementation

ZHANG Ting-wei, YUAN Zheng-wu, ZHOU Mu, TIAN Zeng-shan

(Chongqing Key Lab of Mobile Communications Technology, Chongqing University of Posts and Telecommunications, Chongqing 400065, China)

**Abstract**: According to the coexistence of various communication modes and the development trend, the traditional DDC(Digital Down Converter) structure is modified to apply to the multimode system. The improved construction and parameter design of multimode DDC are proposed, the Verilog coding and Modelsim simulation is completed, and results are analyzed and validated. Finally, code is transplanted into FPGA, and based on the board debugging on the ETTUS RF board, IF board designed independently and Terasic TR4 FPGA board, the feasibility of multimode functionality has been verified. It has been fully proved that this structure can be compatible with two modes (WCDMA and TD-LTE) and has high practicality and generality.

Key words: software radio; multimode terminal; digital down converter; field programmable gate array; intermediate frequency

#### 1 引 言

随着 3G 和 LTE 的不断发展,多模终端将成为 移动终端的发展趋势。多种通信模式的共存对于移 动终端用户而言,就是迫切需要支持多个频段和多 种模式的终端,这样可在多种不同制式的系统之间 自由切换<sup>[1]</sup>。而随着 3G 牌照的发放,3 种不同的 3G 网络覆盖方案共存的局面已经不可避免,再加上目前国内 TD-LTE 正如火如荼地推广,多模终端无疑将成为运营商和终端用户的首选<sup>[2]</sup>。目前,绝大部分移动终端为 GSM 和 3G 的共存,而 TD-LTE 与

<sup>\*</sup> 收稿日期:2013-09-04;修回日期:2013-12-09 Received date:2013-09-04;Revised date:2013-12-09 基金项目:国家自然科学基金资助项目(61301126);重庆市基础与前沿研究计划项目(cstc2013jcyjA40041);重庆邮电大学博士启动基金(A2012-33);重庆邮电大学青年科学研究项目(A2012-77)

Foundation Item: The National Natural Science Foundation of China (No. 61301126); The Foundation and Cutting-edge Research Plan Item of Chongqing (cstc2013jcyjA40041); The Doctor Start-up Foundation of Chongqing University of Posts and Telecommunications (A2012-33); The Youth Science Research Item of Chongqing University of Posts and Telecommunications (A2012-77)

3G 共存的移动终端,在业界仍还处于萌发期。而传统的数字下变频只能实现特定制式的处理,无法实现单系统多模式的功能。

基于此,本文提出一种能够兼容多种模式的数字下变频结构,并且完成各模块 Verilog 代码编写和 Modelsim 仿真;最后将代码移植到 FPGA,并结合 ETTUS 射频板、自主设计的中频板以及友晶 TR4 FPGA 开发板多模硬件平台进行了板级调试,验证了多模功能的可行性。

### 2 改进 DDC 系统结构设计

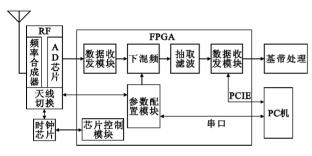

图 1 为设计的多模数字系统结构框图,数字下变频是整个多模系统的核心,完成系统下变频和降采样的任务。

图 1 多模数字系统结构框图

Fig. 1 Structure diagram of multimode digital system

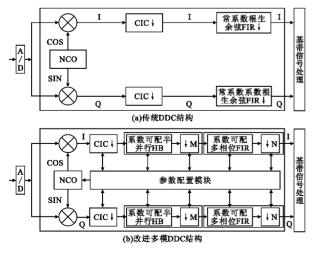

由于传统 DDC 各级滤波器参数一旦配置完成,便无法实时更改,从而大大降低了系统的灵活性,无法满足系统多模需求<sup>[3]</sup>。于是,通过对各模式以及DDC 各模块的分析,对相关模块进行改造,以适应多模系统的需求。图 2 为传统 DDC 结构和改进DDC 结构的对比。

图 2 传统与改进数字下变频结构框图 Fig. 2 Structure diagram of traditional and improved digital frequency conversion

图 2 中,(a) 为传统 DDC 结构,其采用常系数滤波器,无法适用于多频多模需求且处理效果欠佳;而(b) 为改进的多模 DDC 结构,其各级模块参数均可以实时修改,且采用滤波特性较好的半并行 HB 及多相位 FIR 滤波器实现,具有较好的高效性和实用性。

### 3 数字下变频模块设计

数字下变频技术是应用软件无线电系统中的核心技术之一<sup>[3]</sup>。软件无线电的核心思想是:构建一个模块化程度高且开放性强的通用平台,将各种需要实现的功能用软件编程来实现,并使数字化处理(A/D)器件尽可能地靠近射频天线,让所有的信号处理都在数字域中进行<sup>[4]</sup>。

DDC 是数字中频在 A/D 变换后的数字处理部分,可以有效降低采样频率,即通过降低数据量,以达到减轻基带处理对 DSP 计算需求压力的目的<sup>[5]</sup>。下面基于改进的 DDC 结构对各级模块进行阐述。

#### 3.1 NCO 模块设计

NCO 模块能生成一组严格正交、稳定、频率可控的正余弦信号。选用 CORDIC 算法的 IP 核完成 NCO 设计, CORDIC 无需使用乘法器, 只需一个最小的查找表, 利用移位和加法运算, 即可产生高精度正余弦波形, 非常有利于 FPGA 实现<sup>[6]</sup>。 Altera 提供的 IP 核性能卓越, 精度高达 10<sup>-9</sup>, 能够很好地完成下混频的任务。

#### 3.2 CIC 抽取滤波器模块设计

随着现代无线通信中数据传输率不断增加,CIC 滤波器的应用显得尤为重要。CIC 滤波器只包含加法器、积分器和寄存器,没有乘法器,因此适合高采样率电路。此外,CIC 滤波器是一种基于零极点相消的 FIR 滤波器,在高速抽取系统中可以得到有效利用<sup>[6]</sup>。由于 Altera 提供抽取率可变的 CIC IP核,故采用 IP 核完成第一级抽取滤波器设计,可有效缩短开发周期。

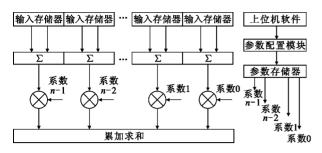

#### 3.3 半并行半带滤波器模块设计

HBF 适用于实现  $D=2^M$ 倍抽取,由于减少了一半存储和计算量,故在高速处理中具有计算效率高,实时性强等优点。常系数 HBF 无法根据制式的不同配置不同特性的滤波器系数,故设计了图 3 所示的可配置半并行 HBF 结构,设置 HBF 各参数为HBF 模块的输入接口,由上位机通过参数配置模块根据所选模式对滤波器参数进行配置,参数可配置是设计的重点。采用这种滤波器完成第二级抽取滤

波的设计,兼顾灵活、速度和资源的有效整合。

图 3 可配置半并行 HBF 实现框图

Fig. 3 Structure diagram of configurable half-parallel filter

图 3 结构的 HBF 滤波器,通过改变抽头系数和 参数存储器中的滤波器系数,还可以将其灵活地运 用于实现高通、带通和带阻滤波器,可移植性好,在 提高系统运算速度和提高系统输入取样率方面具有 很大优势。此结构不仅能实现滤波器参数的灵活配 置,还能提高处理速度和资源消耗。

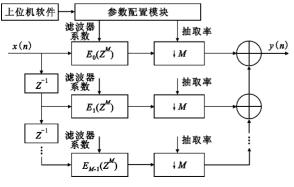

#### 3.4 多相 FIR 滤波器模块设计

因为 HB 滤波器所具有的较大过渡带,不能满足滤波特性的总体设计要求,因此不适合作多级滤波器的最后一级<sup>[3]</sup>。信号经两级抽取滤波后,数据速率比较低,采用具有更高阶频率特性的多相 FIR 滤波器,作为最后一级滤波,具有更好的通带波动、过渡带宽和阻带抑制等性能<sup>[7]</sup>。多相滤波器在信号速率转换过程中去掉不必要的计算,同时在抑制镜像和邻频道干扰上具有较好的性能,可大大提高运算速度和信号质量。为将该滤波器运用于多模DDC 中,设计了图 4 所示可配置多相 FIR 滤波器结构,其参数也是可灵活配置的。其传递函数表达式如式(1)所示:

$$H(z) = \sum_{i=0}^{M-1} z^{-1} E_i(z)$$

(1)

式中,

$$E_i(z) = \sum_{n=0}^{\infty} h(Mn + l)z^{-n}$$

。

图 4 可配置多相 FIR 滤波器实现框图

Fig. 4 Structure diagram of configurable multiphase FIR filter

该结构实现滤波器参数的灵活配置,且运算单 元在输出抽样的周期内的所有时刻都在工作,虽占 用了一定的资源,但大大提高了滤波器的效率。

#### 3.5 参数配置模块设计

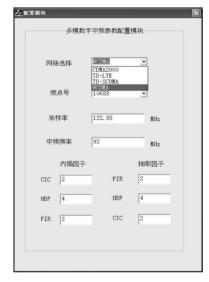

参数配置模块是上位机软件与 FPGA 通信的中间模块,能够根据上位机选择的模式,对系统参数进行对应配置,以满足多种模式系统的需求。参数配置模块将需要配置的接口作为输入,将要设定的参数写入上位机软件中,运行后将参数配置到 FPGA内的参数配置模块对应的寄存器中,从而完成不同模式下系统参数的配置。图 5 给出了参数配置模块的上位机界面。

图 5 参数配置模块的上位机界面

Fig. 5 Computer interface of parameters configuration module

## 4 实验验证及结果分析

#### 4.1 参数分析

由于 3G 制式中 WCDMA 的带宽最宽,其他两种制式原理和 WCDMA 相同,所以主要针对 TD – LTE 和 WCDMA 两种模式进行实验和分析。它们的参数如表 1 所示。

选用 4 种制式码片速率的公倍数245.76 MHz 作为系统时钟频率为数据串并转换提供时钟, 122.88 Msample/s为采样率以便实现整数倍抽取。由于抽取系数较大,若采用一级进行抽取,则滤波器的阶数较高,占用资源较多且不易实现,所以实验采用滤波器分级抽取,以降低滤波器阶数。本设计为3级滤波器,故分解为3级抽取。考虑到 CIC 和 HBF 阶数较小且便于数据率尽快降下来,将抽取系数大的放在前端,故 TD-LTE 系统的 CIC、HB 和 FIR 的抽取

率依次为2、2 和1、WCDMA(2 倍基带速率)系统的

CIC、HB 和 FIR 的抽取率依次为 2、4 和 2。

| 表 1       | TD-LTE 和 W    | VCMDA 下雲  | E频参数      |

|-----------|---------------|-----------|-----------|

| Table 1 D | DC parameters | on TD-LTE | and WCDMA |

| 系统     | 信号带宽<br>/MHz | 基带速率<br>/(Msample/s) | 抽取<br>因子 | 采样率<br>/(Msample/s) | 中频频率<br>/MHz | 系统时钟(FPGA)<br>/MHz | 输入信号<br>比特位/b | 输出信号<br>比特位/b |

|--------|--------------|----------------------|----------|---------------------|--------------|--------------------|---------------|---------------|

| TD-LTE | 20           | 30.72                | 4        | 122.88              | 92           | 245.76             | 14            | 14            |

| WCDMA  | 5            | 3.84                 | 32       | 122.88              | 92           | 245.76             | 14            | 14            |

#### 4.2 软件仿真

根据表 1 设置数字下变频参数,并通过 Modelsim 进行仿真,验证系统可行性。选择 TD-LTE 制式进行可行性验证。考虑到硬件平台的设计,选用 92 MHz的中频频率。由于采用122.88 M的采样率,采样后得到 30.88 MHz 中频信号。NCO产生 30.88 MHz的正余弦信号,作为本振信号,与中频信号相乘,得到零频信号,再经过 CIC、HB 及 FIR 滤波器完成抽取滤波,将数据率降下来。

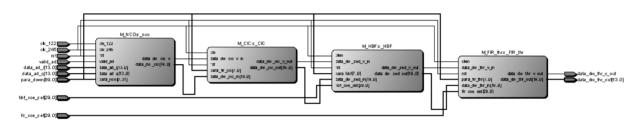

图 6 为 Quartus II 中数字下变频代码的 RTL 级

结构。其中 clk\_122、clk245 是由 AD9510 提供给 DDC 系统的时钟, valid\_ad 为 AD 提供给 DDC 的使能信号, data\_ad\_i、data\_ad\_q 为 AD 采样后的信号, para\_down 为各级抽取率配置人口, hbf\_coe\_set、fir\_coe\_set 分别为 HB、FIR 滤波器的抽头系数配置人口; data\_dw\_thr\_v\_out 为 DDC 输出使能, 同时也是基带处理的使能信号; data\_dw\_thr\_out 则为 DDC 处理之后的信号。完成数字下变频设计后, 进行 Modelsim 功能和时序仿真, 并将每一级输出结果以文本形式保存, 并用 MATLAB 绘制频谱。

图 6 数字下变频模块 RTL 视图 Fig. 6 RTL view of DDC module

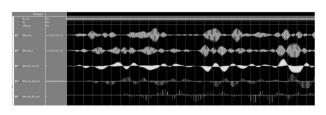

图 7 为数字下变频的功能仿真时序图,data\_ad\_i、data\_ad\_q 分别为 I、Q 两路数据,data\_dw\_cic\_out、data\_dw\_sed\_out、data\_dw\_thr\_out 依次为 CIC、HBF 和 FIR 输出,可以看到每一行输出都晚于上一行信号的输出。由于经滤波抽取处理,采样点逐级降低,但整体信号时域特性相似,将每一级数据保存为文本绘制频谱。

图 7 TD-LTE 的 Modelsim 仿真图 Fig. 7 Modelsim simulation diagram of TD-LTE

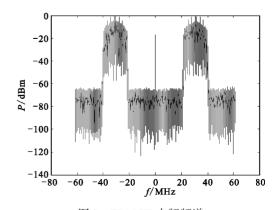

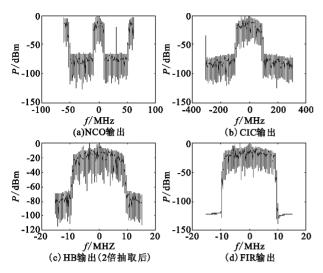

图 8 为 TD-LTE 中频数据频谱,作为 DDC 的数据输入。图 9 为 TD-LTE 系统数字下变频频谱,其

中,(a)为经 NCO 混频后输出信号;(b)为经 CIC 滤波 2 倍抽取后的信号频谱;(c)为半并行 HBF 滤波抽取后的信号频谱,最后经 FIR 滤波后的频谱如(d)所示。可见,信号信噪比较高,带外衰减达120 dB,验证了系统的高效性和可行性。

图 8 TD-LTE 中频频谱 Fig. 8 TD-LTE intermediate frequency spectrum

数字下变频过程频谱 Fig. 9 Spectrums in DDC process

#### 4.3 硬件测试

经 Modelsim 仿真验证后,将代码移植到 FPGA 芯片,通过上位机选择模式配置参数,接收对应模式 数据进行处理。本系统采用 ETTUS 射频板,自主设 计的中频板以及友晶科技 TR4 开发板作为硬件平 台进行实验验证,如图 10 所示。

图 10 数字下变频系统硬件平台 Fig. 10 Hardware platform of DDC

上位机软件选择要接收的模式并配置参数,上 电加载后,信号由射频板天线接收下来,经三级放大 后,由混频电路混频至中频;再经 AD 采样送至 FP-GA 进行数字下变频处理;最后将处理后的数据输 出以文本保存,在 Matlab 中进行同步验证。通过 QUARTUS Ⅱ 的在线逻辑分析仪,监视 FPGA 输入 和输出管脚的状态,如图 11 所示,即为 TD-LTE 数 据管脚的实时状态。

图 11 DDC 各级数据输出状态图

Fig. 11 All leves of state diagram of output data in DDC

上电后,射频端接收相应制式的信号并进行 AD 采样,送给 DDC 处理,将处理结果导出,在 Matlab 中进行同步检测,验证数据的有效性。通过上位 机选择了 WCDMA 和 TD-LTE 模式进行多模验证。

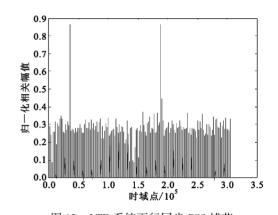

图 12 为 LTE 系统下行同步 PSS 捕获仿真图,对 LTE 系统一帧数据(307 200 个样点)进行仿真,其中 PSS 在一帧中发送两次。从图中可以看到,在 PSS 处 有明显的相关峰值,在峰值处捕获到 PSS,进而完成 下行同步后续步骤,包括时间同步、频偏估计,验证了 经过数字下变频处理以后的数据是有效的。

图 12 LTE 系统下行同步 PSS 捕获 Fig. 12 Downlink synchronization capture for PSS on LTE system

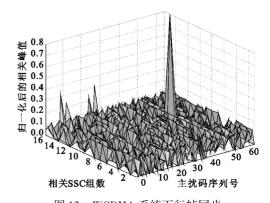

图 13 为 WCDMA 系统下行帧同步仿真图,对 WCDMA 系统实际数据(768 000 个样点)进行仿真。 从图中可以看出,信号与辅助同步信道以及主扰码 有非常明显的相关峰值,在峰值处捕获到帧同步的 位置,进而完成下行同步后续步骤,验证了经过本系 统的数字下变频处理后的数据是有效的。

图 13 WCDMA 系统下行帧同步 Fig. 13 Downlink frame synchronization on WCDMA system

#### 结束语 5

针对目前多种通信模式共存所带来的系统兼容

性问题,而以往研究中同一系统只能完成单一制式处理,于是对传统的数字下变频结构进行了优化改进,使其能够实现兼容多种模式下的数字下变频处理。实验结果表明,经过改进的数字下变频能够有效满足 TD-LTE 和 WCDMA 模式下的数字下变频要求,且无需构架不同模式平台,从而节约了资源,缩短了开发周期,并具有较高的实用性和通用性。针对 GSM、IS95、CDMA2000 以及 TD-SCDMA 等制式,本系统均可以进行处理,对未来 4G、3G 和 2G 的共存提供了平台。

#### 参考文献:

2006. (in Chinese)

[1] 陈明, 周健义, 赵嘉宁. 基于数字中频的多频多模系统的实现[C]//2005 年全国微波毫米波会议论文集(第一册). 深圳:中国电子学会,2006.

CHEN Ming, ZHOU Jian-yi, ZHAO Jia-ning. Implementation of Multi-frequency and Multi-mode system based on DDC[C]// Proceedings of 2005 National Conference on Microwave and Millimeter - wave (Vlume

One). Shenzhen: The Chinese Institute of Electronics,

- [2] 张学军,张孝林. 多模移动终端芯片设计技术及多模 终端发展现状[J]. 移动通信,2006(8):22-24. ZHANG Xue-jun, ZHANG Xiao-lin. Multimode mobile terminal chip design technology and the development situation of multimode terminal[J]. Mobile Communication, 2006(8):22-24. (in Chinese)

- [3] 徐双全,蒋宇中,江海. 数字下变频技术的改进与 FPGA 实现[J]. 无线通信技术,2012,21(4):35-38,43. XU Shuang-quan, JIANG Yu-zhong, JIANG Hai. Improved and implementation of digital down converter based on FPGA [J]. Wireless Communication Technique, 2012,21(4):35-38,43. (in Chinese)

- [4] 张海峰, 赵爱玲. 基于 FPGA 的高速 DUC 设计与高效实现[J]. 电讯技术, 2012, 52(7): 1112-1115.

ZHANG Hai-feng, ZHAO Ai-ling. The design and high

-efficient implementation of high-speed DUC based on

FPGA [J]. Telecommunication Engineering, 2012, 52

(7):1112-1115. (in Chinese)

- [5] Pang L, Zhu B, Chen H, et al. A highly efficient digital down converter in wide band digital radar receiver [C]//

- Proceedings of 2012 IEEE 11th International Conference on Signal Processing, Beijing; IEEE, 2012; 1795–1798.

- [6] 何立志,邱洋,何松. 软件无线电数字下变频技术研究及 FPGA 实现[J]. 电子技术应用,2010,36(11):23-26.

- HE Li-zhi, QIU Yang, HE Song. The research and implementation of Software radio digital down converter technology based on FPGA [J]. Application of electronic technique, 2010, 36(11):23-26. (in Chinese)

- [7] Zhang Q, Su X. The Design of Digital Down Converter Based on FPGA [C]//Proceedings of 2012 8th International Conference on Wireless Communications, Networking and Mobile Computing. Shanghai; IEEE, 2012;1-4.

#### 作者简介:

**张庭伟**(1987—),男,河南人,硕士研究 生,主要研究方向为无线定位技术、软件无线 电技术、数字中频处理;

ZHANG Ting—wei was born in Henan Province, in 1987. He is now a graduate student. His research concerns wireless location technology, software radio technology and digital intermediate

frequency technology.

Email:308089334@ qq. com

**袁正午**(1968—),男,湖南人,博士,教授,主要研究方向为LBS、移动定位、云导航、射线跟踪、GIS系统集成;

YUAN Zheng-wu was born in Hunan Province, in 1968. He is now a professor with the Ph. D. degree. His research concerns LBS, mobile positioning, cloud navigation, ray tracing, and GIS system integration.

Email: yuanzw@ cqupt. edu. cn

田增山(1968—),男,河南人,博士,教授,主要研究方向为个人通信、卫星导航、无线定位、信号检测与处理;

TIAN Zeng-shan was born in Henan Province, in 1968. He is now a professor with the Ph. D. degree. His research concerns personal communications, satellite navigation, wireless location, and signal detecting and processing.

**周** 牧(1984—),男,重庆人,博士(后),副教授,主要研究方向为视觉与无线定位技术、机器学习和凸优化理论。

ZHOU Mu was born in Chongqing, in 1984. He is now an associate professor with the Ph. D. degree. His research concerns visual and wireless location technology, machine learning and convex optimization.